**DESCRIPTION**

IR emitters.

# Vishay Semiconductors

# **Silicon NPN Phototransistor**

VEMT3700F is a high speed silicon NPN epitaxial planar phototransistor in a miniature PLCC-2 package. The

integrated daylight blocking filter is matched to 950 nm

### **FEATURES**

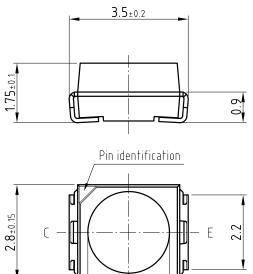

• Package type: surface mount

• Package form: PLCC-2

• Dimensions (L x W x H in mm): 3.5 x 2.8 x 1.75

• High radiant sensitivity

• Fast response times

Daylight blocking filter matched with 870 nm to 950 nm emitters

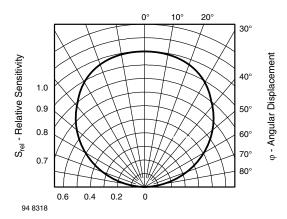

• Angle of half sensitivity:  $\varphi = \pm 60^{\circ}$

- · Package notch indicates collector

- Package matched with IR emitter series VSML3710

- Floor life: 4 weeks, MSL 2a, acc. J-STD-020

- Lead (Pb)-free reflow soldering

- Compliant to RoHS directive 2002/95/EC and in accordance to WEEE 2002/96/EC

#### **APPLICATIONS**

- · Photo interrupters

- Miniature switches

- Counters

- Encoders

- · Position sensors

| PRODUCT SUMMARY |                      |         |                       |  |

|-----------------|----------------------|---------|-----------------------|--|

| COMPONENT       | I <sub>ca</sub> (mA) | φ (deg) | λ <sub>0.5</sub> (nm) |  |

| VEMT3700F       | 0.5                  | ± 60    | 870 to 1050           |  |

#### Note

• Test conditions see table "Basic Characteristics"

| ORDERING INFORMATION |               |                              |              |  |

|----------------------|---------------|------------------------------|--------------|--|

| ORDERING CODE        | PACKAGING     | REMARKS                      | PACKAGE FORM |  |

| VEMT3700F-GS08       | Tape and reel | MOQ: 7500 pcs, 1500 pcs/reel | PLCC-2       |  |

| VEMT3700F-GS18       | Tape and reel | MOQ: 8000 pcs, 8000 pcs/reel | PLCC-2       |  |

#### Note

MOQ: minimum order quantity

| ABSOLUTE MAXIMUM RATINGS (T <sub>amb</sub> = 25 °C, unless otherwise specified) |                                                  |                   |               |      |  |  |

|---------------------------------------------------------------------------------|--------------------------------------------------|-------------------|---------------|------|--|--|

| PARAMETER                                                                       | TEST CONDITION                                   | SYMBOL            | VALUE         | UNIT |  |  |

| Collector emitter voltage                                                       |                                                  | $V_{CEO}$         | 70            | V    |  |  |

| Emitter collector voltage                                                       |                                                  | V <sub>ECO</sub>  | 5             | V    |  |  |

| Collector current                                                               |                                                  | I <sub>C</sub>    | 50            | mA   |  |  |

| Collector peak current                                                          | $t_p/T \le 0.1, t_p \le 10 \mu s$                | I <sub>CM</sub>   | 100           | mA   |  |  |

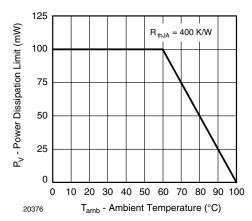

| Power dissipation                                                               |                                                  | P <sub>V</sub>    | 100           | mW   |  |  |

| Junction temperature                                                            |                                                  | Tj                | 100           | °C   |  |  |

| Operating temperature range                                                     |                                                  | T <sub>amb</sub>  | - 40 to + 100 | °C   |  |  |

| Storage temperature range                                                       |                                                  | T <sub>stg</sub>  | - 40 to + 100 | °C   |  |  |

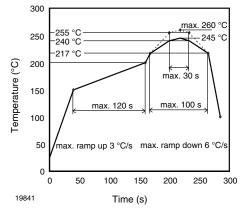

| Soldering temperature                                                           | Acc. reflow solder profile fig. 10               | T <sub>sd</sub>   | 260           | °C   |  |  |

| Thermal resistance junction/ambient                                             | Soldered on PCB with pad dimensions: 4 mm x 4 mm | R <sub>thJA</sub> | 400           | K/W  |  |  |

# Vishay Semiconductors

## Silicon NPN Phototransistor

Fig. 1 - Power Dissipation Limit vs. Ambient Temperature

| <b>BASIC CHARACTERISTICS</b> (T <sub>amb</sub> = 25 °C, unless otherwise specified) |                                                                               |                                |      |             |      |      |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------|------|-------------|------|------|

| PARAMETER                                                                           | TEST CONDITION                                                                | SYMBOL                         | MIN. | TYP.        | MAX. | UNIT |

| Collector emitter breakdown voltage                                                 | I <sub>C</sub> = 1 mA                                                         | V <sub>(BR)CEO</sub>           | 70   |             |      | V    |

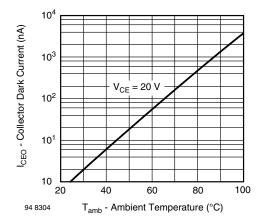

| Collector emitter dark current                                                      | V <sub>CE</sub> = 20 V, E = 0                                                 | I <sub>CEO</sub>               |      | 1           | 200  | nA   |

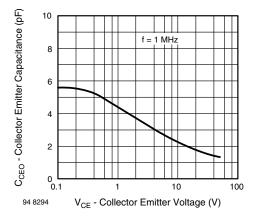

| Collector emitter capacitance                                                       | V <sub>CE</sub> = 5 V, f = 1 MHz, E = 0                                       | C <sub>CEO</sub>               |      | 3           |      | pF   |

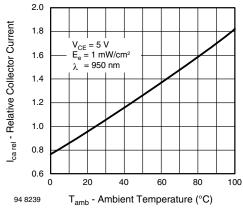

| Collector ligth current                                                             | $E_e$ = 1 mW/cm <sup>2</sup> , $\lambda$ = 950 nm, $V_{CE}$ = 5 V             | I <sub>ca</sub>                | 0.25 | 0.5         |      | mA   |

| Angle of half sensitivity                                                           |                                                                               | φ                              |      | ± 60        |      | deg  |

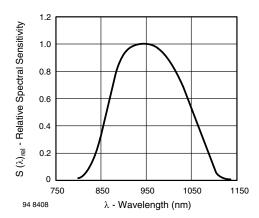

| Wavelength of peak sensitivity                                                      |                                                                               | $\lambda_{p}$                  |      | 940         |      | nm   |

| Range of spectral bandwidth                                                         |                                                                               | λ <sub>0.5</sub>               |      | 870 to 1050 |      | nm   |

| Collector emitter saturation voltage                                                | $E_e = 1 \text{ mW/cm}^2, \ \lambda = 950 \text{ nm}, \ I_C = 0.1 \text{ mA}$ | V <sub>CEsat</sub>             |      | 0.15        | 0.3  | V    |

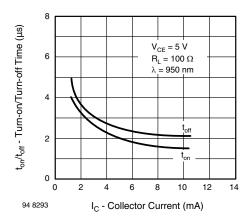

| District Cilities                                                                   | $V_S = 5$ V, $I_C = 1$ mA, $\lambda = 950$ nm, $R_L = 1$ k $\Omega$           | t <sub>r</sub> /t <sub>f</sub> |      | 6           |      | μs   |

| Rise time, fall time                                                                | $V_S = 5$ V, $I_C = 1$ mA, $\lambda = 950$ nm, $R_L = 100~\Omega$             | t <sub>r</sub> /t <sub>f</sub> |      | 2           |      | μs   |

| Cut-off frequency                                                                   | $V_S = 5 \text{ V}, I_C = 2 \text{ mA}, R_L = 100 \Omega$                     | f <sub>c</sub>                 |      | 180         |      | kHz  |

### BASIC CHARACTERISTICS (T<sub>amb</sub> = 25 °C, unless otherwise specified)

Fig. 2 - Collector Dark Current vs. Ambient Temperature

Fig. 3 - Relative Collector Current vs. Ambient Temperature

Vishay Semiconductors

## Silicon NPN Phototransistor

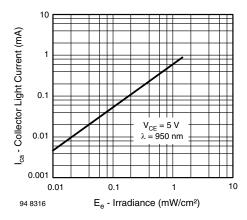

Fig. 4 - Collector Light Current vs. Irradiance

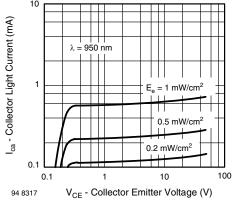

Fig. 5 - Collector Light Current vs. Collector Emitter Voltage

Fig. 6 - Collector Emitter Capacitance vs. Collector Emitter Voltage

Fig. 7 - Turn-on/Turn-off Time vs. Collector Current

Fig. 8 - Relative Spectral Sensitivity vs. Wavelength

Fig. 9 - Relative Radiant Sensitivity vs. Angular Displacement

# Vishay Semiconductors

### Silicon NPN Phototransistor

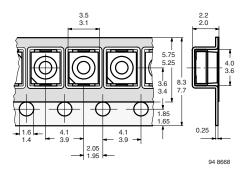

#### **PACKAGE DIMENSIONS** in millimeters

$\phi 2.4$ 3<sup>+0.15</sup>

Drawing-No.: 6.541-5067.03-4

Issue: 1; 30.05.07

#### **Mounting Pad Layout**

### **SOLDER PROFILE**

Fig. 10 - Lead (Pb)-free Reflow Solder Profile acc. J-STD-020

#### **DRYPACK**

Devices are packed in moisture barrier bags (MBB) to prevent the products from moisture absorption during transportation and storage. Each bag contains a desiccant.

#### **FLOOR LIFE**

Floor life (time between soldering and removing from MBB) must not exceed the time indicated on MBB label:

Floor life: 4 weeks

Conditions: T<sub>amb</sub> < 30 °C, RH < 60 %

Moisture sensitivity level 2a, acc. to J-STD-020.

#### **DRYING**

In case of moisture absorption devices should be baked before soldering. Conditions see J-STD-020 or label. Devices taped on reel dry using recommended conditions 192 h at 40 °C (+ 5 °C), RH < 5 %.

#### **TAPE AND REEL**

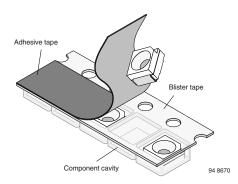

PLCC-2 components are packed in antistatic blister tape (DIN IEC (CO) 564) for automatic component insertion. Cavities of blister tape are covered with adhesive tape.

Fig. 11 - Blister Tape

Fig. 12 - Tape Dimensions in mm for PLCC-2

#### **MISSING DEVICES**

A maximum of 0.5 % of the total number of components per reel may be missing, exclusively missing components at the beginning and at the end of the reel. A maximum of three consecutive components may be missing, provided this gap is followed by six consecutive components.

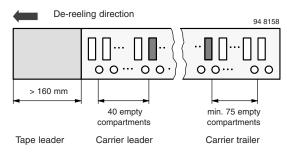

Fig. 13 - Beginning and End of Reel

The tape leader is at least 160 mm and is followed by a carrier tape leader with at least 40 empty compartments. The tape leader may include the carrier tape as long as the cover tape is not connected to the carrier tape. The least component is followed by a carrier tape trailer with a least 75 empty compartments and sealed with cover tape.

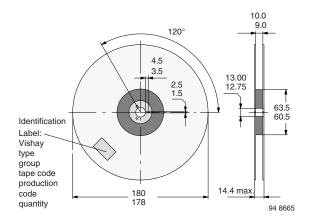

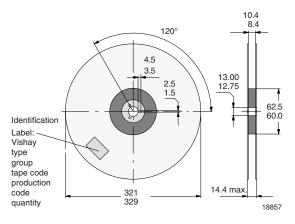

Fig. 14 - Dimensions of Reel-GS08

Fig. 15 - Dimensions of Reel-GS18

#### **COVER TAPE REMOVAL FORCE**

The removal force lies between 0.1 N and 1.0 N at a removal speed of 5 mm/s. In order to prevent components from popping out of the blisters, the cover tape must be pulled off at an angle of 180° with regard to the feed direction.

Vishay

# **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Document Number: 91000 Revision: 18-Jul-08